Ce circuit expérimental préfigure ce que pourrait être les processeurs et les ordinateurs de demain.

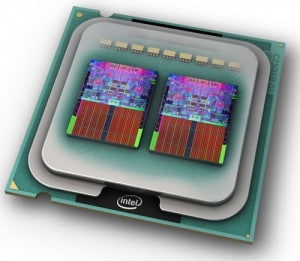

Puce Intel

Les chercheurs des Intel Labs de Bangalore (Inde), Braunschweig (Allemagne) et Hillsboro (Oregon) ont mis au un processeur expérimental, appelé « single-chip cloud computer » (ordinateur monopuce en nuage) par analogie à ce qui se passe dans les centres de données de l’informatique en nuage (cloud computing). Ce circuit futuriste regroupe quarante-huit cœurs, un record pour l’architecture Intel !. Il comporte ainsi dix à vingt fois plus de moteurs de traitements que la plupart des processeurs Intel actuels.

L’objectif à long terme est de doter les futurs ordinateurs d’une échelonnabilité exceptionnelle ouvrant la voie à de nouvelles applications logicielles et à une transformation des interfaces homme-machine, avec pourquoi pas des PC portables dotés d’une capacité de « vision ». Des PC qui n’auraient par exemple plus besoin de claviers. « Avec une puce comme celle-là, on peut imaginer des centres de données consommant dix fois moins que les centres existants, a déclaré Justin Rattner, responsable des Intel Labs et CTO d’Intel, en ajoutant, à terme, j’estime que ces concepts de pointe s’appliqueront aux appareils courants».

Hormis ses quarante-huit cœurs totalement programmables, ce prototype dispose aussi d’un réseau intégré à haute vitesse pour le partage des informations dans un agencement similaire à celui des centres de données utilisés pour créer un « nuage virtuel » de ressources informatiques accessibles via Internet. Sont également incluses des techniques originales de gestion électrique qui permettent à l’ensemble de ses cœurs de travailler à un très haut rendement énergétique, soit à une puissance d’à peine 25 watts au ralenti et 125 watts en performances maximales (environ autant que les processeurs actuels ou l’équivalent de la puissance consommée par deux ampoules domestiques).

Le processeur expérimental a été fabriqué en technologie 45nm. C’est le centre de Braunschweig qui a conçu le cœur du processeur, le réseau qui permet aux cœurs de communiquer avec une latence réduite ainsi qu’un contrôleur mémoire rationalisé et économe en énergie, optimisé pour le multicœur. Les détails de l’architecture seront présentés lors de la conférence ISSCC2010 au mois de février prochain.

Source : Françoise Grosvalet, Electronique International

electronique.biz

Laisser un commentaire